# Communication and Networking Riser Specification Revision 1.2

**Intel Corporation**

## LEGAL NOTICE

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Intel disclaims all liability, including without limitation claims, costs, damages, and expenses arising out of, directly or indirectly, any claim of product liability, personal injury or death, and liability for infringement of any proprietary rights, relating to any use of information in this specification.

THIS SPECIFICATION IS NOT INTENDED TO DIRECT OR INSTRUCT ANY PARTY IN THE DEVELOPMENT OF ANY IMPLEMENTATION WHERE FAILURE OF THE IMPLEMENTATION COULD CAUSE PERSONAL INJURY OR DEATH.

IN NO EVENT WILL INTEL BE LIABLE FOR ANY LOSS OF PROFITS, LOSS OF USE, DIRECT, INCIDENTAL, CONSEQUENTIAL, OR SPECIAL DAMAGES, IRRESPECTIVE OF WHETHER INTEL HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

**Notice:** Implementations developed using the information provided in this specification may infringe the patent rights of various parties including the parties involved in the development of this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party's patents) are granted herein.

\*Other names and brands may be claimed as the property of others.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

For questions on the Communication and Networking Riser Specification or licensing terms please contact Intel by sending e-mail to cnr.support@intel.com.

Copyright® 2000-2001 Intel Corporation. All rights reserved.

# **Table of Contents**

| 1 | Introduction                                                                                                                                                                      |       |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   | 1.1 Related Documents                                                                                                                                                             |       |

| 2 | Architectural Overview                                                                                                                                                            |       |

|   | 2.1 Baseline Riser Architecture                                                                                                                                                   |       |

|   | 2.2 Audio, Modem, and Networking Partitioning                                                                                                                                     |       |

|   | 2.2.1 Audio-Down with Modem and Phone-Line Network-Up Partition                                                                                                                   |       |

|   | 2.2.2 Audio-Down with 10/100 LAN-Up Partition                                                                                                                                     |       |

|   | 2.2.3 Audio-Up, Modem-Up, and Phone-Line Network-Up Partition                                                                                                                     |       |

|   | 2.2.4 Combined Audio/Modem-Up with Phone-Line Network-Up Partition                                                                                                                |       |

|   | 2.2.5 Upgrade To Multi-Channel Audio Partition                                                                                                                                    |       |

|   | 2.3 Unsupported Configurations                                                                                                                                                    |       |

| _ | 2.4 Audio Hardware Scalability Model                                                                                                                                              |       |

| 3 | Electrical Requirements                                                                                                                                                           |       |

|   | 3.1 Signal Names and Pin-out                                                                                                                                                      |       |

|   | 3.1.1 ATX Family Form Factors Signals                                                                                                                                             |       |

|   | 3.1.1.1 Common Signal Description for Type A and Type B Connectors                                                                                                                |       |

|   | 3.1.1.2 Type A Connector Unique Signal Description for the ATX Family Form Factors                                                                                                |       |

|   | 3.1.1.3 Type B Connector Unique Signal Description for the ATX Family Form Factors                                                                                                |       |

|   | 3.1.1.4 Type A Connector Pin Assignments                                                                                                                                          |       |

|   | 3.1.1.5 Type B Connector Pin Assignments                                                                                                                                          |       |

|   | 3.2 Signal Implementation Details                                                                                                                                                 |       |

|   | 3.2.1 CDC_DN_ENAB# Implementation Details                                                                                                                                         |       |

|   | 3.2.1.1 AC '97 Disable and Demotion Rules                                                                                                                                         |       |

|   | 3.2.1.2 CDC_DN_ENAB# Implementation Models                                                                                                                                        |       |

| 4 | 3.3 Communication and Network Riser Interface Electrical Specifications                                                                                                           | . 28  |

| 4 | Power Management and Interface Requirements                                                                                                                                       |       |

|   | 4.1 Power Management.                                                                                                                                                             |       |

|   | 4.1.1 AC '97 Interface Power Management                                                                                                                                           |       |

|   | 4.1.1.1 Split Partition AC '97 and MC '97 CNR Board                                                                                                                               |       |

|   | 4.1.1.2 AMC '97 Combination Codec CNR Board                                                                                                                                       |       |

|   | 4.1.2 LAN Interface Power Management                                                                                                                                              |       |

|   | 4.1.3 USB Interface Power Management and Interface Requirements                                                                                                                   | . 30  |

|   | 4.1.3.1 USB Differential Pair and Over Current Sensing.                                                                                                                           |       |

|   | 4.1.3.2 USB Power Management<br>4.1.4 SMBus Interface Power Management                                                                                                            |       |

|   |                                                                                                                                                                                   |       |

|   | 4.2       Reset Considerations         4.2.1       AC '97 Interface Reset Considerations                                                                                          |       |

|   |                                                                                                                                                                                   |       |

|   | <ul> <li>4.3 AC '97 Clocking Considerations</li> <li>4.3.1 AC '97 ACPI S0 "Working State" Clocking</li> </ul>                                                                     |       |

|   |                                                                                                                                                                                   |       |

| 5 | 4.3.2 AC '97 ACPI S3 and S4 "Sleeping State" Clocking                                                                                                                             |       |

| 5 | Mechanical Requirements                                                                                                                                                           |       |

|   |                                                                                                                                                                                   |       |

|   | <ul><li>5.2 Communication and Networking Riser Board Dimensions</li><li>5.2.1 Board Dimensions for Standard Full Height ATX Family Form Factors</li></ul>                         |       |

|   |                                                                                                                                                                                   |       |

|   | <ul><li>5.2.2 Board Dimensions for Low Profile ATX Family Form Factors</li><li>5.3 Communication and Networking Riser Edge Card Contact for the ATX Family Form Factors</li></ul> |       |

|   | 5.4 Communication and Networking Riser Interface Connector Type                                                                                                                   |       |

|   | 5.4.1 ATX Family CNR Connector Description                                                                                                                                        |       |

|   | 5.4.1 CNR Type A and Type B Connector Physical Requirements                                                                                                                       |       |

|   | 5.4.2 CNR Type A and Type B Connector Performance Requirements                                                                                                                    |       |

|   | 5.5 Communication and Networking Riser I/O Bracket Dimensions                                                                                                                     |       |

|   | 5.5.1 Communication and Networking Riser Full Height I/O Bracket for the ATX Family                                                                                               |       |

|   | 5.5.2 Communication and Networking Riser Low Profile I/O Bracket for the ATX Family                                                                                               |       |

|   | 5.6 Thermal Requirements                                                                                                                                                          |       |

|   | 5.7 EMI, RFI, and Shielding Requirements                                                                                                                                          |       |

| 6 | Operating System, Software, and BIOS Requirements                                                                                                                                 |       |

| 0 | operating system, software, and bros requirements                                                                                                                                 | . т.) |

| 6.1 Operating System Plug-and-Play Requirements                    | 44             |

|--------------------------------------------------------------------|----------------|

| 6.1.1 Plug and Play EEPROM Requirements                            | 44             |

| 6.1.1.1 Plug and Play EEPROM Device Considerations                 |                |

| 6.1.1.2 Plug and Play EEPROM Connectivity                          |                |

| 6.1.2 EEPROM Master Configuration Space                            | 45             |

| 6.1.2.1 EEPROM ID Register (Word 00h)                              |                |

| 6.1.2.2 EEPROM Size Register (Word 02h)                            |                |

| 6.1.2.3 CNR Compliance Register (Word 04h)                         |                |

| 6.1.2.4 AC '97 Compliance Register (Word 06h)                      |                |

| 6.1.2.5 Function ID Register (Word 08h)                            | 47             |

| 6.1.2.6 Reserved Registers (Words 0Ah – 0Ch)                       |                |

| 6.1.2.7 Audio Pointer Register (Word 0Eh)                          |                |

| 6.1.2.8 Modem Pointer Register (Word 10h)                          |                |

| 6.1.2.9 USB Pointer Register (Word 12h)                            |                |

| 6.1.2.10 SMBus Pointer Register (Word 14h)                         |                |

| 6.1.2.11 LAN Pointer Register (Word 16h)                           |                |

| 6.1.2.12 Reserved Pointer Registers (Words 18h – 2Ch)              | 48             |

| 6.1.2.13 Last Valid Address Register (Word 2Eh)                    | 48             |

| 6.1.2.14 Checksum Register (Word 30h)                              |                |

| 6.1.3 Audio Function PnP EEPROM Contents                           |                |

| 6.1.3.1 Audio CNR Vendor ID (Word AP+000h)                         |                |

| 6.1.3.2 Audio CNR Model ID (Word AP+000h)                          |                |

| 6.1.3.3 CNR Multi-Channel Signature (Word AP+004h)                 | ر <del>ب</del> |

| 6.1.3.4 Audio Multi-Channel Model ID (Word AP+006h)                |                |

| 6.1.3.5 Codec x Output Physical Description                        |                |

| 6.1.3.6 Codec x Duput Physical Description                         |                |

| 6.1.4 Modem Function PnP EEPROM Contents                           |                |

| 6.1.4.1 Modern Function Fine EEF ROM Contents                      |                |

| 6.1.4.2 Modem CNR Model ID (Word MP+000h)                          |                |

| 6.1.5 USB Function PnP EEPROM Contents                             |                |

|                                                                    |                |

| 6.1.5.1 USB Option Register (Word UP+00h)                          |                |

| 6.1.5.2 USB Compliance Register (Word UP+002h)                     |                |

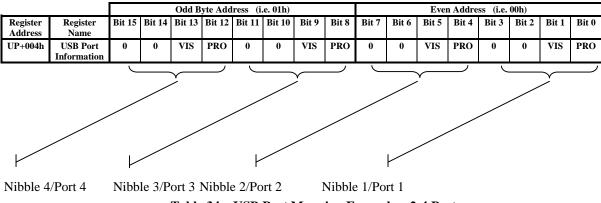

| 6.1.5.3 USB Port Information Register (Word UP+04h)                |                |

| 6.1.6 SMBus Section EEPROM Map                                     |                |

| 6.1.6.1 SMBus Compliance Register (Word SP+000h)                   |                |

| 6.1.6.2 SMBus Function Reserved (Words SP+002h to SP+004h)         |                |

| 6.1.7 LAN Section EEPROM Map                                       |                |

| 6.1.7.1 LAN Option Register (Word LP+000h)                         |                |

| 6.1.7.2 LAN CNR Vendor ID (Word LP+002h)                           |                |

| 6.1.7.3 LAN CNR Model ID (Word LP+004h)                            |                |

| 6.1.7.4 LAN Compliance Register (Word LP+006h)                     |                |

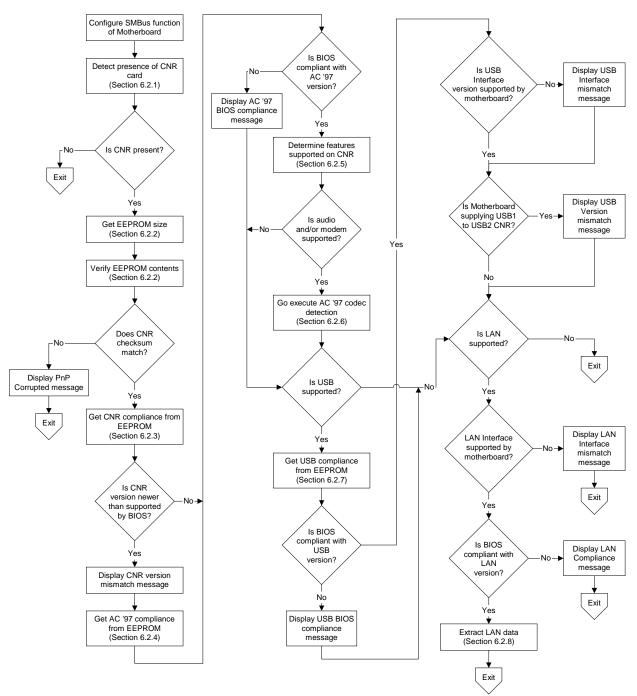

| 6.2 BIOS Requirements                                              |                |

| 6.2.1 CNR Presence Detection                                       |                |

| 6.2.2 Verifying PnP EEPROM Contents                                |                |

| 6.2.3 Verifying CNR Version Compliance                             |                |

| 6.2.4 Verifying AC '97 Version Compliance                          |                |

| 6.2.5 Determining Interfaces Required                              |                |

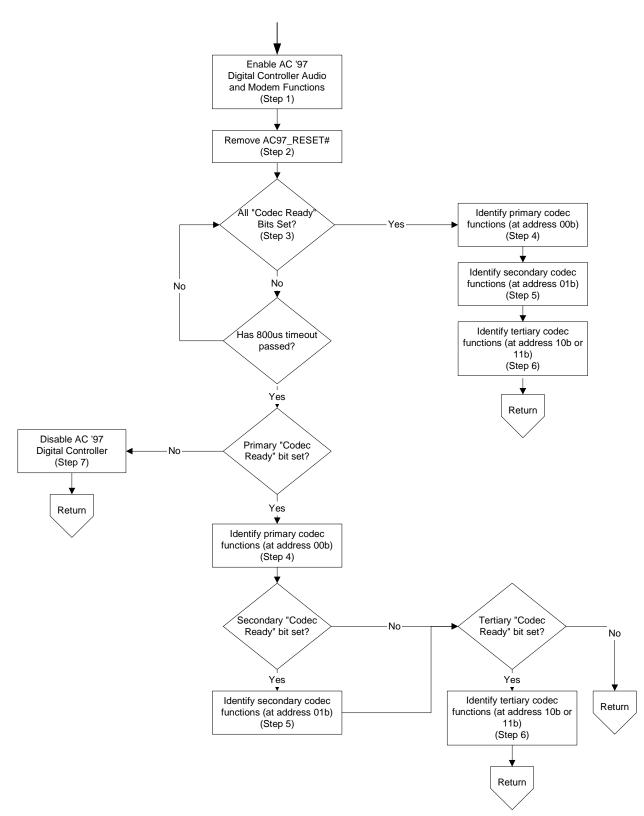

| 6.2.6 AC '97 Audio Codec Detection                                 |                |

| 6.2.6.1 AC '97 Codec Presence and Function Detection               |                |

| 6.2.6.1.1 "Fast Codec Start" Codec Detection Algorithm             |                |

| 6.2.6.1.2 Standard Codec Detection Algorithm                       |                |

| 6.2.6.2 AC '97 Function Enabling and Disabling                     |                |

| 6.2.6.3 AC '97 Plug-and-Play Information Extraction                |                |

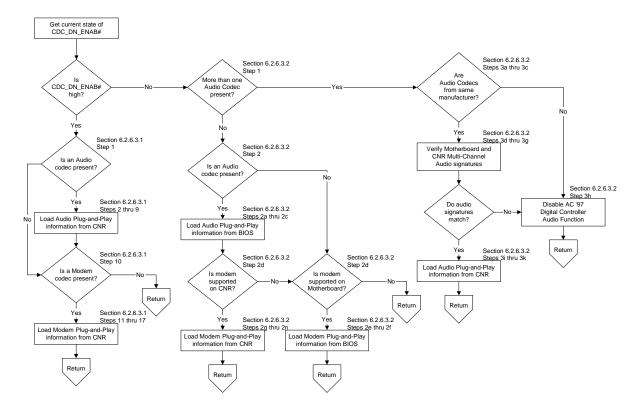

| 6.2.6.3.1 BIOS Steps for Audio Function PnP with CDC_DN_ENAB# High |                |

| 6.2.6.3.2 BIOS Steps for Audio Function PnP With CDC_DN_ENAB# Low  |                |

| 6.2.7 USB Compliance and Options                                   |                |

| 6.2.8 LAN Options                                                  |                |

| 6.3 Software and Driver Requirements                               |                |

| 6.3.1 Audio/Modem Interfacing for Call Progress                    |                |

| November, 2001 Communication and Networking Riser Specification    | Version 1.2    |

| 6.3.2 Multi-Channel Audio Upgrade Considerations               | 78 |

|----------------------------------------------------------------|----|

| 6.3.2.1 Multi-Channel Audio Plug-and-Play Signatures           |    |

| 6.3.2.1.1 Motherboard Multi-Channel Audio Signature Assignment |    |

| 6.3.2.1.2 CNR Multi-Channel Audio Signature Assignment         | 79 |

| 6.3.2.2 Requirements for Multi-Channel Audio Upgrades          | 79 |

| 7 Motherboard Design Rules                                     | 79 |

| 7.1 ATX Family Form Factors Design Rules                       | 79 |

| 8 Communication and Networking Riser Design Rules              |    |

# **List of Figures**

| Figure 1 – Communication and Networking Riser Concept                                           | 9    |

|-------------------------------------------------------------------------------------------------|------|

| Figure 2 – Baseline Communication and Networking Riser                                          |      |

| Figure 3 - Split Partition: Audio-Down with Modem and Phone-Line Network CNR                    | . 12 |

| Figure 4 – Split Codec Partition: Audio-Down with 10/100 LAN CNR                                |      |

| Figure 5 – Split Codec Partition: Audio, Modem, and Phone-Line CNR                              | . 13 |

| Figure 6 – Split Codec Partition: Audio/Modem Codec and Phone-Line Network CNR                  | . 13 |

| Figure 7 – Split Codec Partition: Multi-channel Audio Upgrade CNR                               |      |

| Figure 8 – AC '97 Interface Hardware Acceleration Scalability                                   |      |

| Figure 9 – Type A CNR Connector pin-out for ATX Family Form Factors                             |      |

| Figure 10 – Type B CNR Connector pin-out for ATX Family Form Factors                            | . 23 |

| Figure 11 – AC97_SDATA_IN2 Circuit                                                              |      |

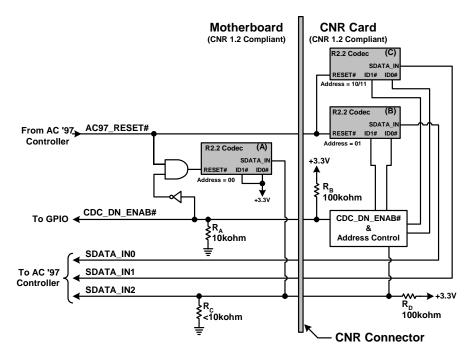

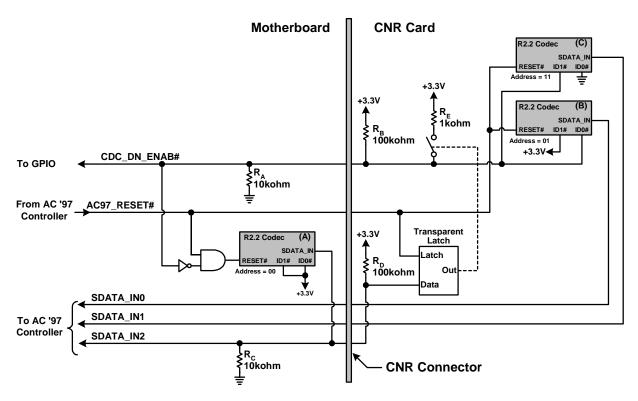

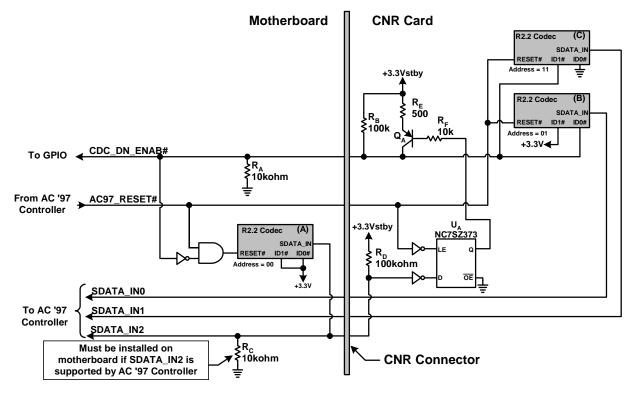

| Figure 12 – CDC_DN_ENAB# & Address Control Block                                                |      |

| Figure 13 – CDC_DN_ENAB# control and Codec Address circuitry                                    |      |

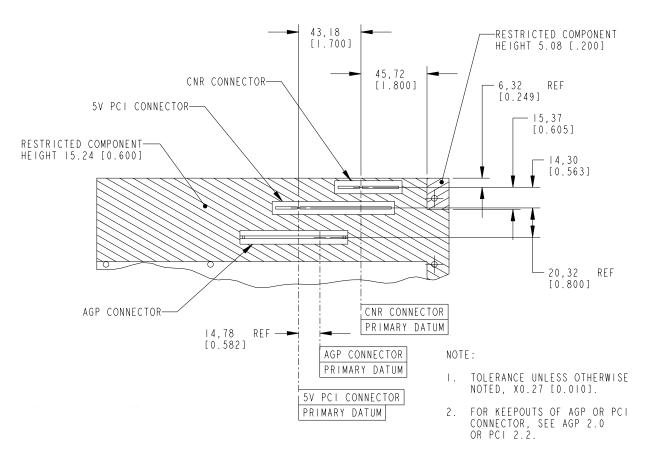

| Figure 14 - CNR Connector location for the ATX Family Form Factors                              | . 33 |

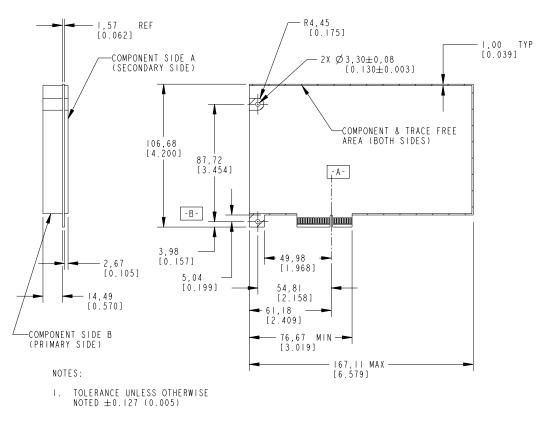

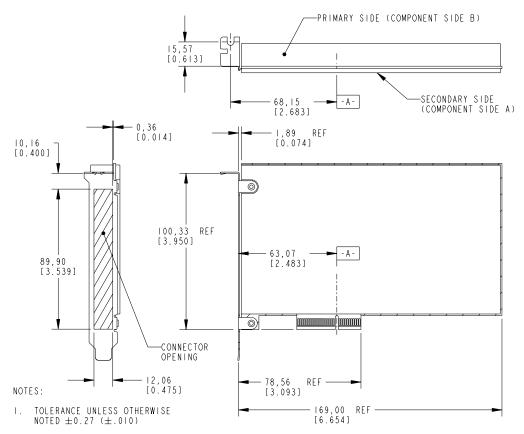

| Figure 15 – Dimensions for a Standard Full Height CNR board                                     | . 34 |

| Figure 16 – Dimensions for a Standard Full Height CNR board with I/O bracket                    | . 35 |

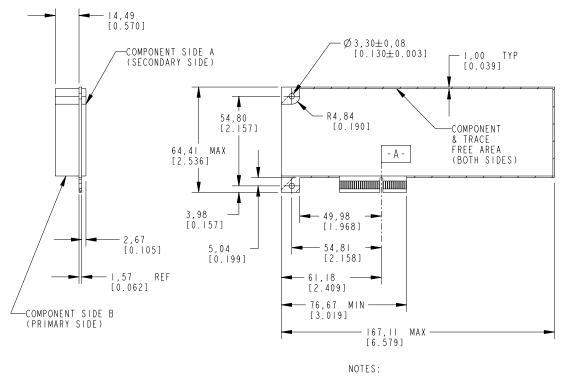

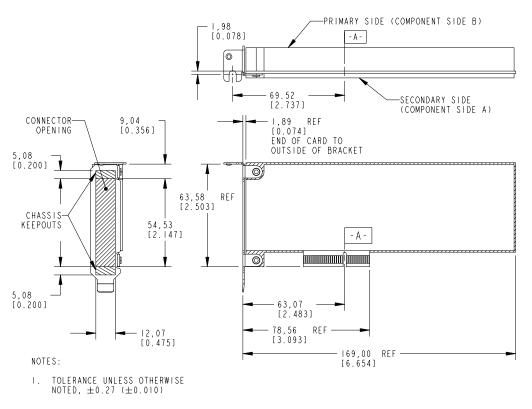

| Figure 17 – Dimensions for Low Profile CNR board                                                | . 36 |

| Figure 18 – Dimensions for Low Profile CNR board with I/O bracket                               |      |

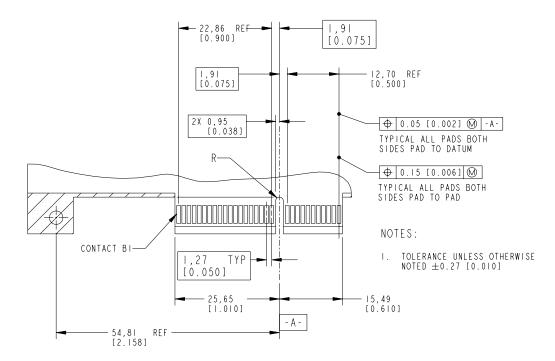

| Figure 19 – Full and Low Profile CNR edge card dimensions                                       | . 37 |

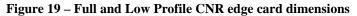

| Figure 20 – CNR Card Edge Connector Contacts                                                    | . 38 |

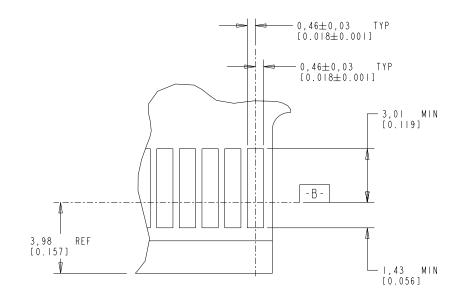

| Figure 21 – CNR Card Edge Connector Bevel                                                       | . 38 |

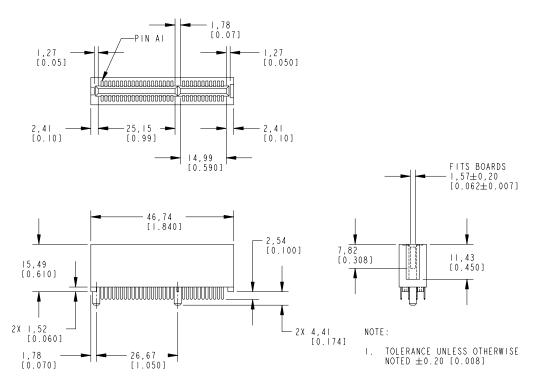

| Figure 22 – CNR Type A and Type B Connector Dimensions                                          | . 39 |

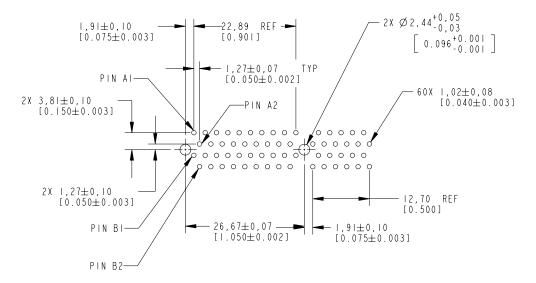

| Figure 23 – CNR Type A and Type B Connector Layout Recommendation                               | . 40 |

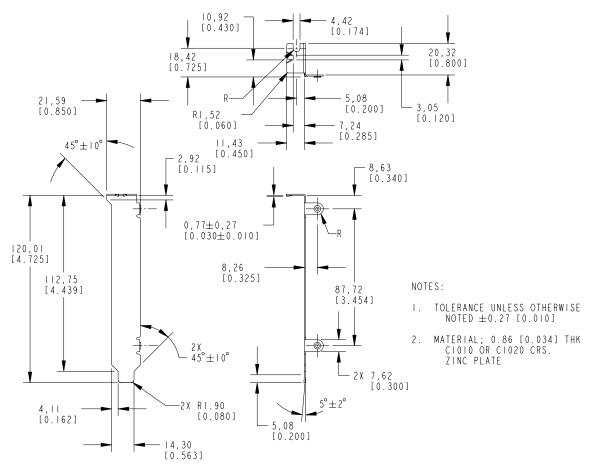

| Figure 24 – Standard Full Height CNR I/O Bracket Dimensions                                     | . 42 |

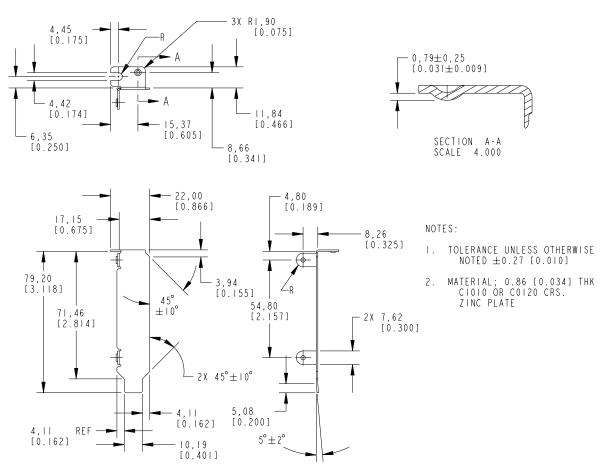

| Figure 25 – Low Profile CNR I/O Bracket Dimensions                                              | . 43 |

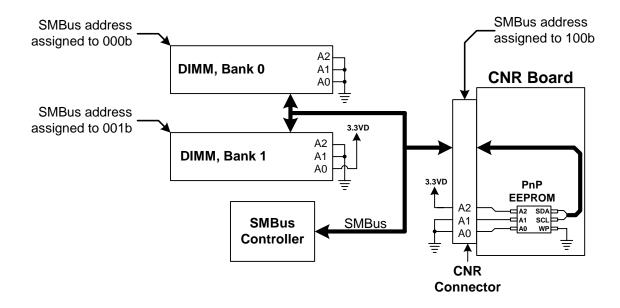

| Figure 26 – SMBus Address Strapping                                                             |      |

| Figure 27 - BIOS Functional Flowchart for CNR Plug-and-Play Support                             | . 59 |

| Figure 28 - AC '97 Presence and Function Detection Flowchart for Fast Codec Start Detection     |      |

| Figure 29 - AC '97 Codec Presence and Function Detection Flowchart for Standard Codec Detection | . 66 |

| Figure 30 – AC '97 Enabling and Disabling Flowchart                                             |      |

| Figure 31 – AC '97 Enabling and Disabling Flowchart continued                                   |      |

| Figure 32 – AC '97 Plug-and-Play Information Flowchart                                          | . 73 |

# **List of Tables**

| Table 1 – CNR Connector signals for the AC '97 Interface                          | 16   |

|-----------------------------------------------------------------------------------|------|

| Table 2 – CNR Connector signals for the USB 2.0 Interface                         | . 17 |

| Table 3 – CNR Connector signals for the SMBus (PnP) EEPROM Interfaces             | . 17 |

| Table 4 – CNR Connector signals for the LAN Interface Microwire EEPROM Interfaces |      |

| Table 5 – CNR Connector power supplies and ground returns                         |      |

| Table 6 – CNR Connector Signals for the Eight-pin PLC LAN Interface               |      |

| Table 7 – CNR Type A Connector Reserved Signals                                   |      |

| Table 8 – CNR Connector Signals for the Seventeen-pin MII LAN Interface           |      |

| Table 9 – CNR Type B Connector reserved signals                                   |      |

| Table 10 – CDC_DN_ENAB# Pull-up Resistor Values                                   |      |

| Table 11 – Communication and Networking Riser Electrical Specification            |      |

| Table 12 – Recommended Power Distribution for the AC '97 Interface Signals        |      |

| Table 13 – Type A and Type B Connector Manufacturers                              |      |

| Table 14 – Type A and Type Connector Physical Requirements                        | . 40 |

| Table 15 – Type A and Type B Connector Mechanical Performance Requirements        |      |

| Table 16 – Type A and Type B Connector Electrical Performance Requirements        | . 41 |

| Table 17 – Type A and Type B Connector Environmental Performance Requirements     |      |

| Table 18 – CNR EEPROM Master Configuration Space Register Map                     |      |

| Table 19 – PnP EEPROM Size Register Value Assignments                             | . 46 |

| Table 20 - CNR Specification Version Mapping in PnP EEPROM                        | . 47 |

| Table 21 – AC '97 Compliance Register Contents                                    | . 47 |

| Table 22 - CNR EEPROM Audio Section Register Map                                  |      |

| Table 23 – Jack Sense Connection                                                  | . 51 |

| Table 24 – S/P-DIF Output Configuration                                           | . 51 |

| Table 25 – S/P-DIF Input Configuration                                            |      |

| Table 26 - CNR EEPROM Modem Section Register Map                                  |      |

| Table 27 - CNR EEPROM USB Section Register Map                                    |      |

| Table 28 – UPCx Bits and Number of Ports                                          |      |

| Table 29 – USB Version to SPD Bit values                                          |      |

| Table 30 - USB Compliance Register Contents                                       |      |

| Table 31 – USB Port Information Register                                          |      |

| Table 32 - USB Port Information Register- Bit Definitions                         |      |

| Table 33 – USB Port Mapping Example – 1 Port                                      |      |

| Table 34 – USB Port Mapping Example – 2:4 Ports                                   |      |

| Table 35 - CNR EEPROM SMBus Section Register Map                                  | . 56 |

| Table 36 – SMBus Compliance Register Contents                                     |      |

| Table 37 – CNR EEPROM LAN Section Register Map                                    |      |

| Table 38 - LAN Compliance Register Contents for eight-pin LAN Interface           |      |

| Table 39 - LAN Compliance Register Contents for seventeen-pin LAN Interface (MII) |      |

| Table 40 – AC '97 Codec Function Mapping to Codec Register Value                  |      |

| Table 41 – Supported Configurations (with CNR installed)                          |      |

| Table 42 – Unsupported Configurations (with CNR installed)                        | . 70 |

## **Revision History**

Version 1.0 - February 7, 2000

• Initial release.

Version 1.1 - October 18, 2000

- Added support for Universal Serial Bus (USB) Revision 2.0

- Incorporated Engineering Change Notices number 1 through 12. The ECN titles are provided below:

- ECN #1: "BIOS Action for LAN Interface Mismatch"

- ECN #2: "BIOS Action for Illegal AC '97 Codec Plug-and-Play Combinations"

- ECN #3: "SVID/SID Persistence During Power Down States"

- ECN #4: "BIOS Messages Pause and Acknowledge"

- ECN #5: "CDC\_DN\_ENAB# Pull-up Resistor Change"

- ECN #6: "Increase Motherboard Keep-out Area"

- ECN #7: "Plug-and-Play EEPROM Compliance and Power Supply Requirement"

- ECN #8: "Clarification on AC '97 Codec Disabling and Demotion Requirements"

- ECN #9: "Update CNR Interface Version Compliance Algorithms"

- ECN #10: "Definition of CNR Pull-up Voltage on CDC\_DN\_ENAB# pin"

- ECN #11: "Optional Main Board AC '97 Codec Disable Circuit"

- ECN #12: "USB\_OC# Pin Voltage Definitions"

Version 1.2 - November 8, 2001

- Added support to AC '97 sections to support three AC '97 codecs, including updating disable and demotion rules, and BIOS AC '97 detection and function algorithms.

- Added additional register definition to the USB section of the CNR PnP EEPROM, in order to better define the USB port usage.

- Added additional register definition to the Audio section of the CNR PnP EEPROM for AC '97 Codec supported input/output jacks.

## 1 Introduction

The Communication and Networking Riser (CNR) Specification defines a hardware scalable Original Equipment Manufacturer (OEM) motherboard riser and interface that supports the audio, modem, Universal Serial Bus (USB), and local area network (LAN) interfaces of core logic chipsets. The main objective of this specification is to reduce the baseline implementation cost of features that are widely used in the "Connected PC", while also addressing specific functional constraints of today's audio, modem, USB, and LAN subsystems.

PC users' demand for feature-rich PCs, combined with the industry's current trend towards lower cost, mandates higher levels of integration at all levels of the PC platform. Motherboard integration of communication technologies has been problematic to date, for a variety of reasons, including FCC and international telecom certification processes, motherboard space, and other manufacturer specific requirements.

Motherboard integration of the audio, modem, USB, and LAN subsystems is also problematic, due to the potential for increased noise, which in-turn degrades the performance of each system. The CNR specifically addresses these problems by physically separating these noise-sensitive systems from the noisy environment of the motherboard.

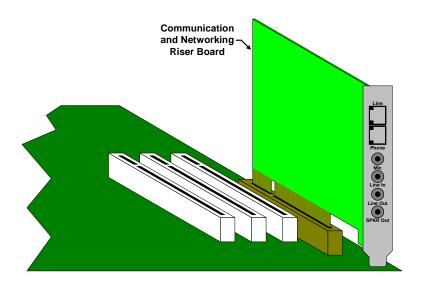

Figure 1 – Communication and Networking Riser Concept

With a standard riser solution, as defined in this specification, the system manufacturer is free to implement the audio, modem, USB, and/or LAN subsystems at a lower bill of materials (BOM) cost than would be possible by deploying the same functions in industry-standard expansion slots or in a proprietary method. With the added flexibility that hardware scalability brings, a system manufacturer has several motherboard acceleration options available, all stemming from the baseline CNR interface.

Note: The CNR Specification does <u>NOT</u> define an aftermarket standard I/O expansion slot. This specification defines a system manufacturer or system integrator, motherboard-only, riser interface, which is to be fully configured prior to the initial shipment of the system. Standard I/O expansion slots, such as those supported by the PCI bus architecture, are intended to continue serving as the retail channel upgrade medium.

The CNR Specification describes interfaces that can support multi-channel audio, V.90 analog modem, phone-line based networking, 10/100 Ethernet based networking, as well as expandability for future technologies.

This specification defines the CNR architecture, required electrical characteristics of the riser interface, mechanical, and thermal requirements. The CNR Specification supports the ATX, microATX, and FlexATX form factors (now referred to as ATX family form factors). This specification does <u>NOT</u> support the NLX form factor. Future versions or revisions of this specification may support additional form factors, as they become available and/or widely used by the PC industry.

## Note: Questions regarding the Communication and Networking Riser Specification may be sent, via e-mail, to:

## cnr.support@intel.com

## **1.1 Related Documents**

- "Audio Codec '97 Component Specification, Revision 2.1" (http://developer.intel.com/pc-supp/platform/ac97)

- "ACPI (Advanced Configuration and Power Interface) Specification" (<u>http://www.acpi.info/index.html</u>)

- "PCI Bus Power Management Interface Specification, Revision 1.1" (<u>http://www.pcisig.com</u>)

- "Instantly Available PC Power Management Design Guide" (http://developer.intel.com/design/power/pcpower.htm)

- "Universal Serial Bus Specification, Revision 2.0" (<u>http://www.usb.org</u>)

- "System Management Bus Specification, Revision 1.1" (http://www.smbus.org/)

- "PCI Local Bus Specification, Revision 2.2" (<u>http://www.pcisig.com</u>)

- "ATX Specification, Version 2.03" (<u>http://www.formfactors.org/</u>)

- "microATX Motherboard Interface Specification, Version 1.0" (<u>http://www.formfactors.org/</u>)

- "Accelerated Graphics Port (AGP) Specification, Revision 2.0" (<u>http://developer.intel.com/technology/agp</u>)

## 2 Architectural Overview

The following sections provide an overview of the baseline architecture along with descriptions of both supported and unsupported CNR configurations. Included in the following sections are different configurations of audio, modem, and LAN subsections, either up on the CNR board or physically soldered down on the motherboard printed circuit board (PCB). In addition, a model for hardware scalability of the audio subsystem is described.

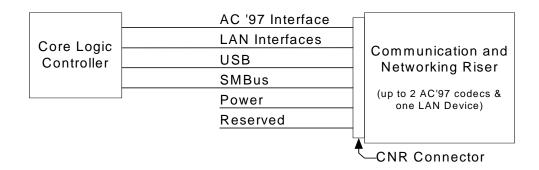

Figure 2 – Baseline Communication and Networking Riser

## 2.1 Baseline Riser Architecture

Figure 2 illustrates the baseline architecture of a motherboard with support for a CNR Connector and board.

The backbone of the CNR interface consists of an AC '97-compliant AC-Link, a LAN interface, an SMBus\* interface, and a USB\* 2.0 interface.

- AC '97 Interface: Used to support audio and/or modem functions on the CNR board.

- LAN Interfaces: Provides one of two LAN interfaces for networking functions. Interfaces include an eight-pin interface for use with platform LAN connection (PLC) based devices, and a seventeen-pin interface for Media Independent Interface (MII) based devices (commonly referred to as a PHY).

- USB Interface: Used to support technologies or functions that are being implemented on a USB 2.0 Interface.

- SMBus Interface: Used specifically to provide Plug-and-Play functionality for the CNR board.

Additional signals on the CNR interface support:

- **Power:** Signals that are required to support power management, as well as the main power supplies to operate the CNR board silicon and support circuitry.

- **Reserved:** Signals that will be used to support future features and power supply requirements.

## 2.2 Audio, Modem, and Networking Partitioning

In the CNR architecture there are several different ways to partition the audio, modem, USB, and LAN subsystems. Ultimately, the decision as to how the partitioning occurs is up to the system integrator. This decision is further based on the system integrators' needs for feature set and management of the various motherboard and CNR designs.

When selecting a partition, the system integrator must consider the user model for implementing audio, modem, USB, and LAN technologies. In the consumer and small business environments, the networking technology may be a phone line based network connected to an RJ-11 jack. This network, along with a traditional analog modem provides for convergence of the network and communication systems at the RJ-11 jack. Thus, the system integrator should consider how the user would connect the analog modem and home phone networks to the phone wiring in the building. In the corporate environment, the analog modem will most likely not exist, but instead a traditional 10/100 Ethernet based LAN would be implemented. In this case, the LAN usually connects to an RJ-45 connector, thus simplifying the user model.

The following section shows some of the possible partitioning options for the audio, modem, and LAN subsystems between the motherboard PCB and the CNR board. Note that these are only a few examples of the numerous partitioning scenarios.

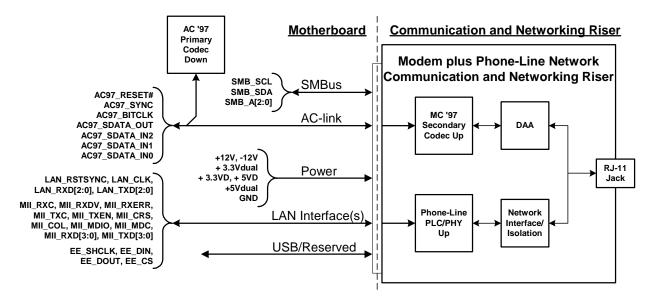

## 2.2.1 Audio-Down with Modem and Phone-Line Network-Up Partition

The configuration in Figure 3 deploys the audio codec on the motherboard with both the modem codec and phoneline PLC/PHY device on the CNR board. This configuration provides the flexibility to design the motherboard independent of the CNR board, thus decoupling government regulatory certification of the riser from the motherboard. In addition, a single motherboard design can then be used in a system targeted at either the consumer or commercial markets, depending on the CNR board installed.

Figure 3 – Split Partition: Audio-Down with Modem and Phone-Line Network CNR

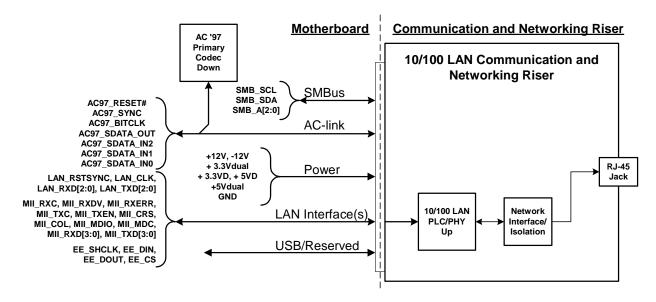

## 2.2.2 Audio-Down with 10/100 LAN-Up Partition

The configuration in Figure 4 deploys the audio codec on the motherboard with the 10/100 Ethernet based LAN PLC/PHY device on the CNR board. This configuration also provides the flexibility of allowing a single motherboard to be used in a system targeted at either the consumer or commercial markets depending on the CNR board installed.

Figure 4 – Split Codec Partition: Audio-Down with 10/100 LAN CNR

## 2.2.3 Audio-Up, Modem-Up, and Phone-Line Network-Up Partition

The configuration in Figure 5 places the audio, modem, and phone-line networking components on the CNR board. In this configuration, the motherboard could be a minimally featured board, in which the system manufacturer has the opportunity to populate a fully featured riser, or a subset of a fully featured riser.

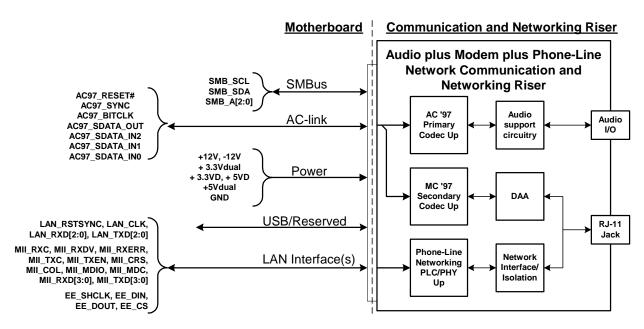

Figure 5 – Split Codec Partition: Audio, Modem, and Phone-Line CNR

## 2.2.4 Combined Audio/Modem-Up with Phone-Line Network-Up Partition

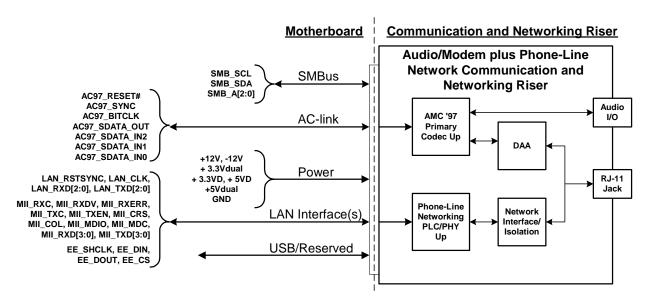

The configuration in Figure 6 employs an AMC '97 combined audio/modem codec with a Phone-line PLC/PHY device. This configuration introduces a higher level of integration and potentially a lower implementation cost for the audio, modem, and LAN subsystems.

Figure 6 – Split Codec Partition: Audio/Modem Codec and Phone-Line Network CNR

## 2.2.5 Upgrade To Multi-Channel Audio Partition

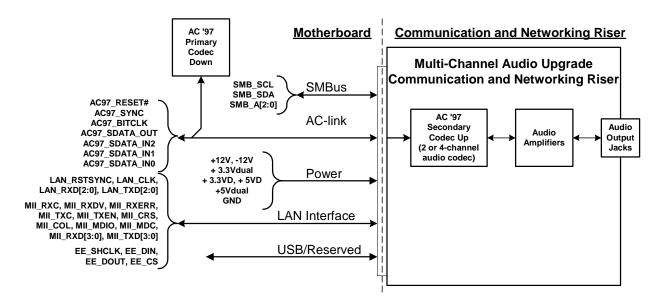

The configuration in Figure 7 deploys the audio codec on the motherboard with an additional audio codec on the CNR board. This configuration demonstrates the flexibility of allowing a single motherboard to accept an audio upgrade from two-channel audio (stereo) to multi-channel audio (four or six channels) by simply installing a CNR board.

Figure 7 – Split Codec Partition: Multi-channel Audio Upgrade CNR

## 2.3 Unsupported Configurations

All CNR configurations **must** be limited to a single primary AC '97 codec, with up to two additional secondary AC '97 codecs. Any CNR configuration with more than a single primary AC '97 codec is unsupported, and will likely result in improper system behavior and/or component damage. The required support for CDC\_DN\_ENAB# pin functionality ensures that only one primary codec can ever reside on the AC-link for a given CNR configuration. Refer to Table 1 (and Section 3.2.1) for details on implementing the functionality of the CDC\_DN\_ENAB# signal.

As the LAN Interfaces are designed to support a single PLC/PHY device, the motherboard <u>must not</u> be designed to simultaneously support both a PLC/PHY device on the motherboard and additional PLC/PHY devices on the CNR board. In addition, the CNR must not be designed to simultaneously support more than a single PLC/PHY device. Failure to follow these requirements may cause damage to devices attached to the LAN Interfaces, due to contention on the signals of the LAN interfaces. Detailed information on the LAN interfaces can be found in the appropriate Core Logic Specification.

## 2.4 Audio Hardware Scalability Model

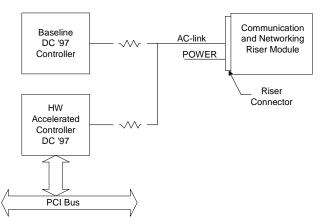

The baseline CNR architecture supports an "in-line" hardware acceleration model for both the audio and modem subsystems. In-line acceleration is the optimum form of hardware acceleration. An in-line accelerator is situated between the source of the pre-processed data and the final destination for the processed data. An accelerator fetches pre-processed data directly from main memory, processes it, and then passes it directly to the codec(s) via the AC-Link.

A system manufacturer may design their motherboard with provisions to support a baseline controller with a stuffing option for a PCI-based hardware-accelerated controller. The following figure illustrates the CNR architecture's support for hardware acceleration.

Figure 8 – AC '97 Interface Hardware Acceleration Scalability

The CNR architecture's hardware scalability enables a system manufacturer to choose which controller to deploy as the master of the AC-Link. The "selectable" controller arrangement, utilizing series resistors<sup>1</sup>, provides a simple method for an accelerated controller to fully replace the baseline controller. From the perspective of the CNR board, an AC '97-compliant controller is mastering the AC-Link. The CNR board cannot discern whether it is being mastered by the baseline or accelerated controller.

At motherboard design time, a system manufacturer may design in provisions for a certain hardware-accelerated controller solution which, when mated with the capabilities of compatible CNR board, creates a range of possible motherboard solutions.

Note: The CNR architecture does <u>not</u> support after-market audio, modem, or LAN upgrades by only changing the CNR board. Once a system manufacturer or system integrator has shipped a system into the field, regardless of the motherboard/CNR board configuration capabilities, all future audio, modem, and/or LAN upgrades <u>must</u> be brought into the system via industry-standard expansion vehicles such as a PCI slot, Universal Serial Bus (USB) port, or through OEM upgrades.

## **3** Electrical Requirements

## 3.1 Signal Names and Pin-out

The CNR connector is the interface between the motherboard and the CNR board. The connector provides all of the necessary signals to support several different configurations of audio, modem, USB, and/or LAN subsystems in the system, as previously mentioned.

The CNR provides support for two different LAN interfaces; an eight-pin PLC interface or a seventeen-pin interface (commonly known as MII or IEEE 802.3u). Support for these two interfaces is provided on two separate CNR connector pin-outs. The pin-out for the eight-pin LAN interface is defined in the Type A CNR connector (Figure 9), while the pin-out for the seventeen-pin LAN interface is defined in the Type B CNR connector (Figure 10).

## 3.1.1 ATX Family Form Factors Signals

The following sections provide detailed information regarding the signals on both the Type A and Type B CNR connectors, including signal names, descriptions, and pin number assignments for the ATX Family Form Factors.

For the following sections the signals designated as Input are sourced from the motherboard, while signals designated as Output are sourced from the CNR board. Those signals defined as In/Out may be sourced from either the motherboard or the CNR board.

$<sup>^{1}</sup>$  The resistor values should be chosen for the best signal quality. The baseline controller's resistor values may not necessarily be the same value as those of the accelerated controller.

## 3.1.1.1 Common Signal Description for Type A and Type B Connectors

This section describes the signals, which are common to both the Type A and Type B CNR connectors for the ATX Family Form Factors. The following tables are broken into sections to describe the signals on an interface-by-interface basis.

# *Note:* It is strongly recommended that all of the signals listed in the following tables, if implemented on and not in use by devices on the motherboard, be routed to, and implemented on the Type A and Type B CNR connector.

| Signal<br>Name | Туре   | Pin<br>Number | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC97_BITCLK    | In/Out | B30           | Serial data clock from primary codec to AC '97 Controller and any non-primary codecs. The nominal frequency of this signal is 12.288 MHz. For detailed information, refer to the current version of the AC '97 Component Specification. AC97_BITCLK is an output from a primary codec and an input to non-primary codecs. The reset state of this signal must meet the requirements of the current version of the AC '97 Component Specification.                                                                                      |

| AC97_SYNC      | Input  | B28           | Synchronization pulse from an AC '97-compliant controller to all of the AC '97-<br>compliant codecs on the AC link. This signal is nominally a 1.3 $\mu$ S wide pulse,<br>which is used to synchronize the AC link. For detailed information, refer to the<br>current version of the AC '97 Component Specification. The reset state of this<br>signal must meet the requirements of the current version of the AC '97 Component<br>Specification.                                                                                     |

| AC97_SDATA_OUT | Input  | B29           | AC '97 serial data from an AC '97-compliant controller to all of the AC '97-<br>compliant codecs on the link. For detailed information, refer to the current version<br>of the AC '97 Component Specification. The reset state of this signal must meet the<br>requirements of the current version of the AC '97 Component Specification.                                                                                                                                                                                              |

| AC97_SDATA_IN0 | Output | A29           | AC '97 serial data from a primary AC '97-compliant codec to an AC '97-compliant<br>Controller. For detailed information, refer to the current version of the AC '97<br>Component Specification. The reset state of this signal must meet the requirements<br>of the current version of the AC '97 Component Specification.                                                                                                                                                                                                             |

| AC97_SDATA_IN1 | Output | A28           | AC '97 serial data from an AC '97-compliant codec (primary or secondary) to an AC '97-compliant Controller. For detailed information, refer to the current version of the AC '97 Component Specification. The reset state of this signal must meet the requirements of the current version of the AC '97 Component Specification.                                                                                                                                                                                                      |

| AC97_SDATA_IN2 | Output | A27           | AC '97 serial data from an AC '97-compliant codec (primary or secondary) to an AC '97-compliant Controller. For detailed information, refer to the current version of the AC '97 Component Specification. The reset state of this signal must meet the requirements of the current version of the AC '97 Component Specification. This signal may not be present in all AC '97 Controllers. Refer to Section 3.3.1.2 for information on designing with AC '97 Controllers supporting two or three codecs.                              |

| AC97_RESET#    | Input  | A26           | Active low AC '97 link reset signal. For detailed information, refer to the current version of the AC '97 Component Specification. The reset state of this signal must meet the requirements of the current version of the AC '97 Component Specification.                                                                                                                                                                                                                                                                             |

| CDC_DN_ENAB#   | In/Out | B26           | CDC_DN_ENAB# indicates whether the motherboard or the CNR is in control, or mastering, the AC '97 interface attached to the CNR Connector. When at a logic low level, the CDC_DN_ENAB# signal indicates that the primary codec on the motherboard is active and controlling the AC '97 Interface. In addition, the CNR will, when CDC_DN_ENAB# is low, demote its codecs to the next available address and to the next available SDATA_IN signal. See Section 3.2.1 for more details on the implementation of the CDC_DN_ENAB# signal. |

|                |        |               | When at a logic high level, the CDC_DN_ENAB# signal indicates that a primary codec on the CNR is taking control of the AC '97 Interface. In addition, the motherboard will, when CDC_DN_ENAB# is high, disable all of its codecs. See Section 3.2.1 for more details of how to implement the CDC_DN_ENAB# signal.                                                                                                                                                                                                                      |

|                |        |               | CDC_DN_ENAB# is an input to the AC '97 Controller, but should be connected to a GPIO pin for debug purposes.                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Table 1 – CNR Connector signals for the AC '97 Interface

| Signal<br>Name | Туре   | Pin<br>Number | Signal Description                                                                                                                                                                                                |

|----------------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB+           | In/Out | A13           | Positive side of the differential USB data signal. For more information, refer to the Universal Serial Bus Specification. The state of this signal during reset must meet the Universal Serial Bus Specification. |

| USB-           | In/Out | A15           | Negative side of the differential USB data signal. For more information, refer to the Universal Serial Bus Specification. The state of this signal during reset must meet the Universal Serial Bus Specification. |

| USB_OC#        | Output | B16           | USB bus over-current signal. For more information, refer to the Universal Serial<br>Bus Specification 2.0. The state of this signal during reset must meet the Universal<br>Serial Bus Specification 2.0.         |

| Signal<br>Name | Туре   | Pin<br>Number | Signal Description                                                                                                                                                                                                                                                                                                             |

|----------------|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMB_SCL        | Input  | B25           | Serial clock line from the SMBus master to SMBus slave device(s) on the CNR board. For detailed information on this signal, refer to the current version of the System Management Bus Specification. The reset state of this signal must meet the current version of the System Management Bus Specification.                  |

| SMB_SDA        | In/Out | A25           | Bi-directional serial data line between the SMBus master to SMBus slave device(s) on the CNR board. For detailed information on this signal, refer to the current version of the System Management Bus Specification. The reset state of this signal must meet the current version of the System Management Bus Specification. |

| SMB_A2         | Input  | A24           | This signal is bit 2 (MSB) of the 3-bit address of the SMBus EEPROM on the CNR board. Refer to Section 6.1.1.2 for detailed information on the connectivity of this signal. The state of this signal during reset must be the SMBus address for the CNR board.                                                                 |

| SMB_A1         | Input  | A23           | This signal is bit 1 of the 3-bit address of the SMBus EEPROM on the CNR board.<br>Refer to Section 6.1.1.2 for detailed information on the connectivity of this signal.<br>The state of this signal during reset must be the SMBus address for the CNR board.                                                                 |

| SMB_A0         | Input  | B24           | This signal is bit 0 (LSB) of the 3-bit address of the SMBus EEPROM on the CNR board. Refer to Section 6.1.1.2 for detailed information on the connectivity of this signal. The state of this signal during reset must be the SMBus address of the CNR board.                                                                  |

| Table 3 CND    | Connector | signals for | the SMBuc  | (DnD)    | <b>EEPROM Interfaces</b> |

|----------------|-----------|-------------|------------|----------|--------------------------|

| Table 5 – CINK | Connector | signals for | the Swidus | (1 III ) | LEI KOWI IIIteriates     |

| Signal<br>Name | Туре   | Pin<br>Number | Signal Description                                                                                                                                                                                                                                                                                                                    |

|----------------|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EE_SHCLK       | Input  | B22           | This signal is the serial clock signal from the core logic MAC Microwire* interface to the Microwire EEPROM (which stores MAC/PLC/PHY specific information) on the CNR board.                                                                                                                                                         |

| EE_DIN         | Input  | A21           | This signal carries serial data from the core logic MAC Microwire* interface to the Microwire EEPROM (which stores MAC/PLC/PHY specific information) on the CNR board. The EE_DIN signal on the CNR connector must be connected to the DIN pin on the Microwire EEPROM.                                                               |

| EE_DOUT        | Output | B21           | This signal carries serial data from the Microwire EEPROM (which stores MAC/PLC/PHY specific information) on the CNR board to the core logic MAC Microwire* interface. The EE_DOUT signal on the CNR connector must be connected to the DOUT pin on the Microwire EEPROM.                                                             |

| EE_CS          | Input  | A22           | The CNR board uses this signal to enable the serial EEPROM devices on the CNR board. When EE_CS is high (one) the Microwire EEPROM (for the LAN Interface) becomes active. When EE_CS is low (zero) the EEPROM is inactive. The resting state of this signal is low (zero). The state of this signal during reset must be low (zero). |

## Table 4 – CNR Connector signals for the LAN Interface Microwire EEPROM Interfaces

| Signal    |        | Pin    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name      | Туре   | Number | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| +12V      | Supply | A16    | Positive 12-volt main power supply                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -12V      | Supply | B18    | Negative 12-volt main power supply                                                                                                                                                                                                                                                                                                                                                                                                                                |

| +5VD      | Supply | A19    | Positive 5-volt main digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                         |

| +3.3VD    | Supply | B19    | Positive 3.3-volt main digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                       |

| +5Vdual   | Supply | B15    | Positive 5-volt main/standby power supply (can be used for USB power). +5Vdual supply provides full-rated power capacity during working or full-on state, and a limited power capacity during sleep or suspended states. When a +5Vdual supply is not available, this pin <u>must</u> be connected to a +5 volt standby power source. This signal <u>must not</u> be connected to a +5VD, as doing so eliminates the possibility of deep-sleep wake capabilities. |

| +3.3Vdual | Supply | A18    | Positive 3.3-volt main/standby power supply. +3.3Vdual supply provides full-rated power capacity during working or full-on state, and a limited power capacity during sleep or suspended states. When +3.3Vdual is not available, this pin <u>must</u> be connected to a +3.3-volt standby power source. This signal <u>must not</u> be connected to a +3.3VD, as doing so eliminates the possibility of deep-sleep wake capabilities.                            |

| Ground    | Ground | A3     | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | A6     | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | A9     | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | A14    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | A17    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | A20    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | A30    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B4     | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B7     | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B10    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B13    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B17    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B20    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B23    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ground    | Ground | B27    | Power supply and signal ground return path.                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 5 – CNR Connector power supplies and ground returns

## 3.1.1.2 Type A Connector Unique Signal Description for the ATX Family Form Factors

This section describes the signals unique to the Type A CNR connector for the ATX Family Form Factors.

*Note:* It is <u>strongly</u> recommended that all of the signals listed in the following tables, if implemented on and not in use by devices on the motherboard, be routed to, and implemented on the Type A CNR connector.

| Signal<br>Name | Туре   | Pin<br>Number | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN_CLK        | Output | A10           | Data clock from a LAN Interface compliant PLC to the Media Access Controller (MAC). The nominal frequency of this signal determines the data transfer rate between the PLC and the MAC. For detailed information, refer to the current version Core Logic Design Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification. |

| LAN_RSTSYNC    | Input  | B9            | This is a dual function pin that provides either a reset pulse or a synchronization<br>pulse from the MAC to the LAN Interface compliant PLC. For detailed information<br>on this signal, refer to the current version of the Core Logic Design Specification.<br>The reset state of this signal must meet the requirements set forth in the current<br>version of the Core Logic Design Specification.            |

| LAN_TXD2       | Input  | A7            | Bit 2 (MSB) of the 3-bit data bus transferring data from the MAC to the LAN<br>Interface compliant PLC. For detailed information on this signal, refer to the current<br>version of the Core Logic Design Specification. The reset state of this signal must<br>meet the requirements set forth in the current version of the Core Logic Design<br>Specification.                                                  |

| LAN_TXD1       | Input  | B8            | Bit 1 of the 3-bit data bus transferring data from the MAC to the LAN Interface compliant PLC. For detailed information on this signal, refer to the current version of the Core Logic Design Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                                    |

| LAN_TXD0       | Input  | A8            | Bit 0 (LSB) of the 3-bit data bus transferring data from the MAC to the LAN<br>Interface compliant PLC. For detailed information on this signal, refer to the current<br>version of the Core Logic Design Specification. The reset state of this signal must<br>meet the requirements set forth in the current version of the Core Logic Design<br>Specification.                                                  |

| LAN_RXD2       | Output | B11           | Bit 2 (MSB) of the 3-bit data bus transferring data from the LAN Interface<br>compliant PLC to the MAC. For detailed information on this signal, refer to the<br>current version of the Core Logic Design Specification. The reset state of this signal<br>must meet the requirements set forth in the current version of the Core Logic Design<br>Specification.                                                  |

| LAN_RXD1       | Output | A11           | Bit 1 of the 3-bit data bus transferring data from the LAN Interface compliant PLC device to the MAC. For detailed information on this signal, refer to the current version of the Core Logic Design Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                             |

| LAN_RXD0       | Output | B12           | Bit 0 (LSB) of the 3-bit data bus transferring data from the LAN Interface compliant PLC device to the MAC. For detailed information on this signal, refer to the current version of the Core Logic Design Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                       |

Table 6 - CNR Connector Signals for the Eight-pin PLC LAN Interface

| Signal<br>Name | Туре | Pin<br>Number | Signal Description |

|----------------|------|---------------|--------------------|

| Reserved       | N/A  | A1            | Reserved           |

| Reserved       | N/A  | A2            | Reserved           |

| Reserved       | N/A  | A4            | Reserved           |

| Reserved       | N/A  | A5            | Reserved           |

| Reserved       | N/A  | A12           | Reserved           |

| Reserved       | N/A  | B1            | Reserved           |

| Reserved       | N/A  | B2            | Reserved           |

| Reserved       | N/A  | B3            | Reserved           |

| Reserved       | N/A  | B5            | Reserved           |

| Reserved       | N/A  | B6            | Reserved           |

| Reserved       | N/A  | B14           | Reserved           |

## Table 7 – CNR Type A Connector Reserved Signals

## 3.1.1.3 Type B Connector Unique Signal Description for the ATX Family Form Factors

This section describes the signals unique to the Type B CNR connector for the ATX Family Form Factors.

*Note:* It is <u>strongly</u> recommended that all of the signals listed in the following tables, if implemented on and not in use by devices on the motherboard, be routed to, and implemented on the Type B CNR Connector.

| Signal<br>Name | Туре   | Pin<br>Number | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII_RXD3       | Output | A12           | Bit 3 (MSB) of the 4-bit data bus transferring data from the MII compliant PHY to<br>the MAC. For detailed information on this signal, refer to the current version of the<br>Core Logic Design Specification and the IEEE 802.3u Specification. The reset state<br>of this signal must meet the requirements set forth in the current version of the Core<br>Logic Design Specification.                                           |

| MII_RXD2       | Output | B11           | Bit 2 of the 4-bit data bus transferring data from the MII compliant PHY to the MAC. For detailed information on this signal, refer to the current version of the Core Logic Design Specification and the IEEE 802.3u Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                             |

| MII_RXD1       | Output | A11           | Bit 1 of the 4-bit data bus transferring data from the MII compliant PHY to the MAC. For detailed information on this signal, refer to the current version of the Core Logic Design Specification and the IEEE 802.3u Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                             |

| MII_RXD0       | Output | B12           | Bit 0 (LSB) of the 4-bit data bus transferring data from the MII compliant PHY to the MAC. For detailed information on this signal, refer to the current version of the Core Logic Design Specification and the IEEE 802.3u Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                       |

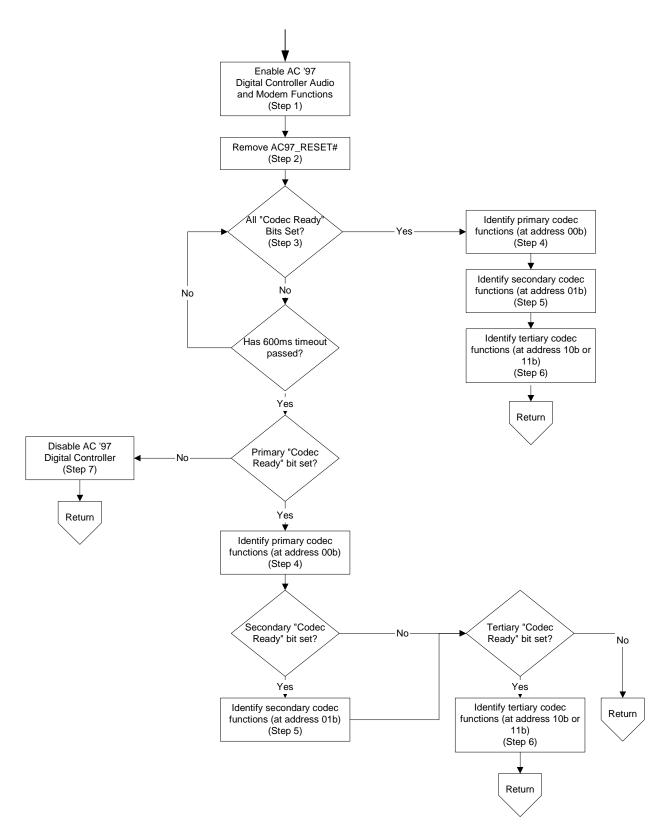

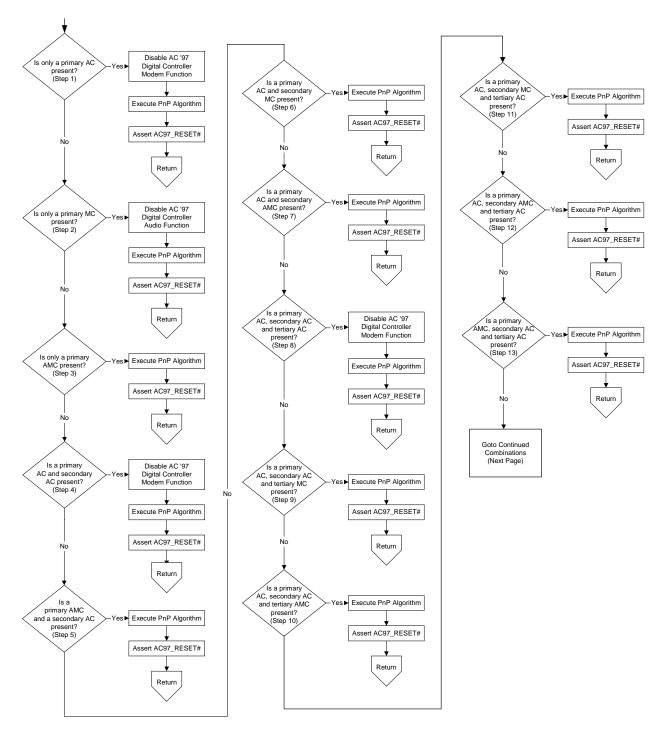

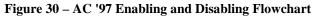

| MII_RXC        | Output | A5            | Data clock from a MII Interface compliant PHY to the MAC. For detailed information, refer to the current version Core Logic Design Specification and the IEEE 802.3u Specification. The reset state of this signal must meet the requirements set forth in the current version of the Core Logic Design Specification.                                                                                                              |